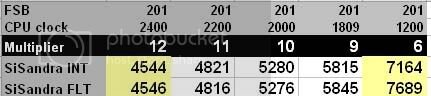

Here are some interesting SiSoft Sandra results. I was testing the memory bandwidth of TCCD using SiSoft Sandra and found that decreasing the multi increased the performance significantly. At multi 6 the FLT was close to 7700! I'm not sure if this is an error in the SiSoft Sandra program or if the bandwidth of the RAM is truly inversely proportional to the cpu speed. Does increasing the speed of the Dothan really decrease the bandwidth of the memory?

Hopefully someone with another chip where the mutiplier can be changed can confirm these results. I would like to know a few things:

1. Is this specific to Dothan chips?

2. Is this an error in Sisoft Sandra?

3. If its not an error, why is there almost a 50% increase in bandwidth from multi 12 to 6?

Any input would be appreciated.

Hopefully someone with another chip where the mutiplier can be changed can confirm these results. I would like to know a few things:

1. Is this specific to Dothan chips?

2. Is this an error in Sisoft Sandra?

3. If its not an error, why is there almost a 50% increase in bandwidth from multi 12 to 6?

Any input would be appreciated.