- Joined

- Jun 14, 2010

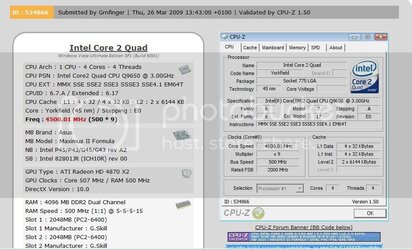

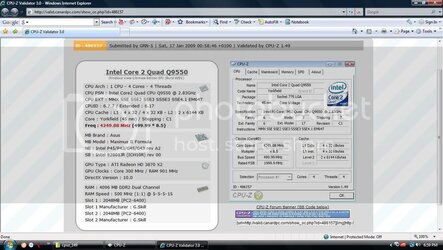

take me goes to at , FSB 500 or 4.5GHz , please , now that here , consult for go to build with , , thank ,

3.99GHz

Extreme Tweaker

Ai Overclock Tuner : Manual

OC From CPU Level Up : AUTO

CPU Ratio Control : Manual

- Ratio CMOS Setting : 8.5

FSB Frequency : 470

CPU Clock Skew : Normal

North Bridge Clock Skew : Normal

FSB Strap to North Bridge : 333

DRAM Frequency: DDR2-1129

Dram Clock Skew CH1 A1 : Advanced 300ps

DRAM Clock Skew CH1 A2 : Normal

Dram Clock Skew CH1 B1 : Advanced 300ps

Dram Clock Skew CH1 B2 : Normal

DRAM Timing Control: Manual

CAS# Latency : 5

RAS# to CAS# Delay : 5

RAS# Precharge : 5

RAS# ActivateTime : 15

RAS# to RAS# Delay : 3

Row Refresh Cycle Time : 55

Write Recovery Time : 6

Read to Precharge Time : 3

Read to Write Delay (S/D) : 8

Write to Read Delay (S) : 3

Write to Read Delay (D) : 5

Read to Read Delay (S) : 4

Read to Read Delay (D) : 6

Write to Write Delay (S) : 4

Write to Write Delay (D) : 6

Write to PRE Delay : 14

Read to PRE Delay : 5

PRE to PRE Delay : 1

ALL PRE to ACT Delay : 5

ALL PRE to REF Delay : 5

DRAM Static Read Control: Enabled

Dram Read Training : Disabled

MEM OC Charger : Enabled

Ai Clock Twister : Stronger

Transaction Booster : Manual

Common Performance Level [8]

Pull-In of CHA PH1 Disabled

Pull-In of CHA PH2 Disabled

Pull-In of CHA PH3 Disabled

Pull-In of CHA PH4 Disabled

Pull-In of CHA PH5 Disabled

Pull-In of CHB PH1 Disabled

Pull-In of CHB PH2 Disabled

Pull-In of CHB PH3 Disabled

Pull-In of CHB PH4 Disabled

Pull-In of CHB PH5 Disabled

PCIE Frequency : 101

CPU Voltage : 1.35000

CPU PLL Voltage : 1.53975

FSBT : 1.33850

DRAM Voltage : 2.21075

North Bridge Voltage : 1.39150

South Bridge Voltage 1.5 : 1.5

South Bridge Voltage 1.1 : 1.1

CPU GTL Reference 0 : Auto

CPU GTL Reference 1 : -45mv

CPU GTL Reference 2 : Auto

CPU GTL Reference 3 : -45mv

North Bridge GTL Reference : AUTO

DDR2 Channel A REF Voltage : AUTO

DDR2 Channel B REF Voltage : AUTO

North Bridge DDR Reference : AUTO

Load Line Calabration : Enabled

CPU Sread Spectrum : Disabled

PCIE Spread Spectrum : Disabled

3.99GHz

Extreme Tweaker

Ai Overclock Tuner : Manual

OC From CPU Level Up : AUTO

CPU Ratio Control : Manual

- Ratio CMOS Setting : 8.5

FSB Frequency : 470

CPU Clock Skew : Normal

North Bridge Clock Skew : Normal

FSB Strap to North Bridge : 333

DRAM Frequency: DDR2-1129

Dram Clock Skew CH1 A1 : Advanced 300ps

DRAM Clock Skew CH1 A2 : Normal

Dram Clock Skew CH1 B1 : Advanced 300ps

Dram Clock Skew CH1 B2 : Normal

DRAM Timing Control: Manual

CAS# Latency : 5

RAS# to CAS# Delay : 5

RAS# Precharge : 5

RAS# ActivateTime : 15

RAS# to RAS# Delay : 3

Row Refresh Cycle Time : 55

Write Recovery Time : 6

Read to Precharge Time : 3

Read to Write Delay (S/D) : 8

Write to Read Delay (S) : 3

Write to Read Delay (D) : 5

Read to Read Delay (S) : 4

Read to Read Delay (D) : 6

Write to Write Delay (S) : 4

Write to Write Delay (D) : 6

Write to PRE Delay : 14

Read to PRE Delay : 5

PRE to PRE Delay : 1

ALL PRE to ACT Delay : 5

ALL PRE to REF Delay : 5

DRAM Static Read Control: Enabled

Dram Read Training : Disabled

MEM OC Charger : Enabled

Ai Clock Twister : Stronger

Transaction Booster : Manual

Common Performance Level [8]

Pull-In of CHA PH1 Disabled

Pull-In of CHA PH2 Disabled

Pull-In of CHA PH3 Disabled

Pull-In of CHA PH4 Disabled

Pull-In of CHA PH5 Disabled

Pull-In of CHB PH1 Disabled

Pull-In of CHB PH2 Disabled

Pull-In of CHB PH3 Disabled

Pull-In of CHB PH4 Disabled

Pull-In of CHB PH5 Disabled

PCIE Frequency : 101

CPU Voltage : 1.35000

CPU PLL Voltage : 1.53975

FSBT : 1.33850

DRAM Voltage : 2.21075

North Bridge Voltage : 1.39150

South Bridge Voltage 1.5 : 1.5

South Bridge Voltage 1.1 : 1.1

CPU GTL Reference 0 : Auto

CPU GTL Reference 1 : -45mv

CPU GTL Reference 2 : Auto

CPU GTL Reference 3 : -45mv

North Bridge GTL Reference : AUTO

DDR2 Channel A REF Voltage : AUTO

DDR2 Channel B REF Voltage : AUTO

North Bridge DDR Reference : AUTO

Load Line Calabration : Enabled

CPU Sread Spectrum : Disabled

PCIE Spread Spectrum : Disabled

Last edited: