martinus said:

good on ya, DSTA, we seem to have the same understanding of the data sheet.

German saying: "two fools, one idea"

.

Perhaps it's time to re-read the S370 Universal Platform design guide...

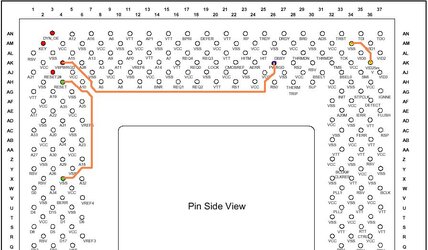

vid4 to me is the corresponding pin of the VRM specification up to 8.4. It only exists on slot 1 according to intel, and serves to select voltages 2.1V and higher. Of course it is present on any VRM IC up to version 8.4, and the funny thing is, some socket mobos seem to route it through to pin AK36 which should be GND according to intel.

I have also checked the VIA C3 data sheets, where AK36 is specified as GND, too.

Good idea on checking the C3 data sheet. I always forget about those. Speaking of VIA: I've noticed that Asus says not all their "Slotkets" are compatible with VIA chipsets. Anyone an idea why this could be the case? Don't have an actual problem with that, just curious.

Back to the VRM issue: you are right that AK36 should be GND according to the spec sheet, but perhaps AK36 was a VID pin in some earlier Intel spec sheet or design guide or perhaps an application note from the VRM supllier.

IMVHO mobo makers don't think half as much about their products as we enthousiasts would believe them to do. They got a working VRM design from a slot 1 mobo in the drawer, they'll re-use it if they can slap it on a S370 board.

-#-

@jae87:

GND (ground? i wonder if this is the same as Vss??

Yup. I think so.

AGTL+ I/O and AGTL I/O ...

I think the "+" denotes the older GTL spec (1.5V vtt), without "+" it's the newer spec introduced with Tualatin.

According to Intel, certain steppings of Coppermine are compatible with both the new AGTL and the older AGTL+ spec, so that's probably why they use both terms AGTL+ and AGTL in the spec sheet.

About DYN_OE:

"The DYN_OE allows the BSEL and VID signals to be driven out from the processor.

When this signal is low (a condition that will occur if the Intel® Pentium® III

processor is installed in a non-supported platform), the VID and BSEL signals will

be tri-stated and the platform pull-up resistors will set the VID and BSEL to all ‘1’s’

which is a safe setting. This signal must be connected to a 1k? resistor to VTT.

Refer to the platform design guide for implementation detail and resistor tolerance."

If I understand this correctly, this is another way to make sure Tualatins don't start up on older boards. If VID is set to "all 1" this tells the VRM "no juice, 0V".

About Tualatin with 256K cache and SMP:

I'm pretty pessimistic about it. Don't think it will work with anything other than a P3-S -- would be a dream come true for me though, I've got a GA-6BXD somewhere and am currently using an MS-6120 (with 450 MHz P2s)...

To get an understanding of how the BREQ stuff works, here's a piece from

Ars Technica.

Now if you look at the Tualatin Celeron spec sheet, BR1, which was on pin X2 for the P3-S, is labled as "reserved". Could be that it's still there, but could also be disabled.

Funnily, for the P3 Tualatin with 256K cache (which also has no official SMP), the datasheet still lists BR1 as available and maps this to pin X2, just as it was for Coppermine and is now for P3-S.

I fear this is an omission in the spec sheet, though: IMO, Intel used the re-design they had to do to shrink coppermine to 0.13 as opportunity to cripple or otherwise disable SMP on those chips for good, just like they did with Celeron-II.