- Joined

- Jan 10, 2012

I seem to have, once again, proven that I know nothing, this time about pcie stuff.

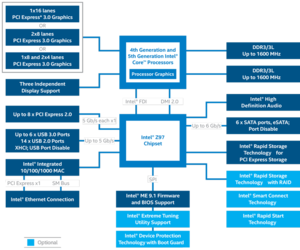

looking at the intel site it would appear that my z97/4790K rigs have 16 pcie "lanes" in the cpu and 8 more "lanes" someplace in the chipset.

I would have thought that they would be someplace buried in the motherboard, like memory traces, what and where are these pcie lanes?

this stems from my failing to figure out that on my asrock Z97extreme9/4790K rigs that I don't have enough of these things to run sli and an NVMe drive.......... sad.........

looking at the intel site it would appear that my z97/4790K rigs have 16 pcie "lanes" in the cpu and 8 more "lanes" someplace in the chipset.

I would have thought that they would be someplace buried in the motherboard, like memory traces, what and where are these pcie lanes?

this stems from my failing to figure out that on my asrock Z97extreme9/4790K rigs that I don't have enough of these things to run sli and an NVMe drive.......... sad.........