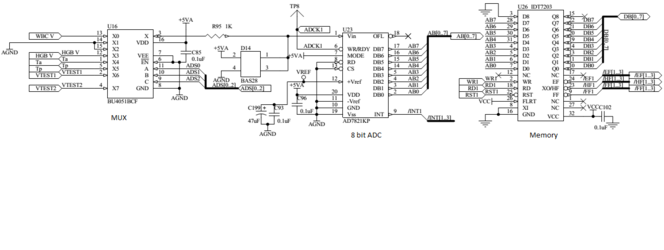

I am referring to schematics where 8 bit parallel ADC is interfaced to IDT7203 (datasheet can be seen here http://www.kynix.com/Detail/735739/IDT7203.html)Asynchronous FIFO Memory. It is used for storing ADC results. Schematics as shown:

Now if I replace it with sync FIFO buffer (by replacing 8 to 12 bit ADC and 12 or 16 bit memory), Can I do that? Is there any disadvantage to use Synchronous memory?

Thanks in advance.

Now if I replace it with sync FIFO buffer (by replacing 8 to 12 bit ADC and 12 or 16 bit memory), Can I do that? Is there any disadvantage to use Synchronous memory?

Thanks in advance.