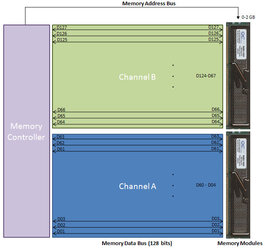

I am trying to understand the correlation between system RAM used in dual channel, and the multiple pathways used on GPUs. So a 128-bit GPU has four RAM modules, two of which are in parallel to increase capacity, right? So each module is 32 bit, and they are DDR modules, so they operate with 64 "effective bits (32 bit x2 transfers per clock cycle)," and with two groups of RAM modules in parallel (two RAM modules in parallel with two more), we get an "effective" transfer of 128 bit. Okay, so how is that any different than standard "dual channel" system RAM? It's not, right? Both dual channel DDR3 and 128-bit GDDR5 cards essentially operate in "dual channel" mode, right?

So then if we extend this scenario to 192-bit GPUs, those operate the same way as triple channel system RAM, no? And 256-bit cards are effectively "quadruple" channel, right?

Last, if my 192-bit cards are effectively "triple channel," why is the effective speed of the RAM 6000 MHz. and the speed in Precision X listed as 3000 MHz? Shouldent the individual RAM modules be 1/3rd the effective speed, so 2000MHz.?

So then if we extend this scenario to 192-bit GPUs, those operate the same way as triple channel system RAM, no? And 256-bit cards are effectively "quadruple" channel, right?

Last, if my 192-bit cards are effectively "triple channel," why is the effective speed of the RAM 6000 MHz. and the speed in Precision X listed as 3000 MHz? Shouldent the individual RAM modules be 1/3rd the effective speed, so 2000MHz.?

Last edited: