- Joined

- Sep 7, 2003

I've been reading a lot about SS and SOI but something is confusing me here.

I read how each one allows for higher clock speeds by upto **%. But does it allow you to go smaller. What I'm saying is, are they moving smaller just because they can lower the voltage, and also put up the clock, or are they going smaller JUST because you have to in order to use SS or SOI?

I hope that wasn't too confusing.

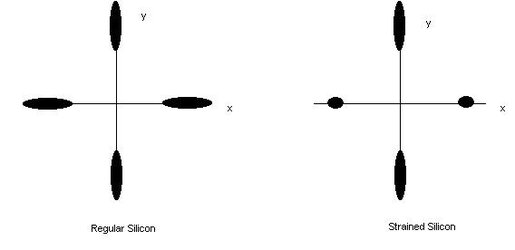

SS = Strained Silicon

SOI = Silicon On Insulator

I read how each one allows for higher clock speeds by upto **%. But does it allow you to go smaller. What I'm saying is, are they moving smaller just because they can lower the voltage, and also put up the clock, or are they going smaller JUST because you have to in order to use SS or SOI?

I hope that wasn't too confusing.

SS = Strained Silicon

SOI = Silicon On Insulator