So I read through the JEDEC GDDR5 Standard document, and it turns out you're half right. GDDR5 has two clocks: CK and WCK. The "effective clock" that's listed on websites like Newegg is the CK frequency.

Commands are registered on the rising edge of the CK clock. This means that it executes commands once per cycle. Addresses are registered on rising and falling edges of the CK clock. This is "double pumped".

Data (be it read or write) is clocked on the rising and falling edges of WCK. WCK is double the speed of CK.

There is no quad pumping in GDDR5. There are just two separate clocks both can be double pumped. The memory bandwidth comes from the fact that you get 2 bits of data transferred every WCK clock.

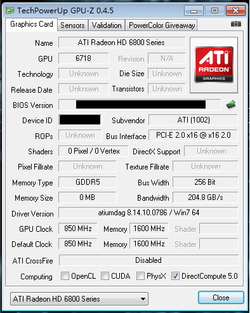

So if a GPU is listed as 1200MHz effective memory clock on Newegg, it means the following:

CK Clock: 1200MHz

Effective command clock: 1200MHz

Effective addressing clock: 2400MHz

WCK Clock: 2400MHz

Effective data clock: 4800MHz

"Memory bandwidth": 4.8Gbps.

I put that in quotes because its far from the true bandwidth. The memory can't constantly read in a stream of data. It's mostly limited by the latencies which are on the order of 8 CK clocks.

So yes, the data is read in at 4800MHz, but the operating clock of the memory is still 1200MHz.

Sources:

http://www.jedec.org/sites/default/files/docs/JESD212.pdf

http://www.hynix.com/datasheet/eng/...1=01&menu2=04&menu3=05&menuNo=1&m=3&s=5&RK=26

its a monster i tel you !

its a monster i tel you !

its a monster i tel you !

its a monster i tel you !