-

Welcome to Overclockers Forums! Join us to reply in threads, receive reduced ads, and to customize your site experience!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

3770K IHS removal and results

- Thread starter graysky

- Start date

- Joined

- Apr 11, 2010

- Location

- London, UK

I found CLP but branded by Phobya 30% cheaper. On photos it looks exactly the same.

yer i saw that, seems the same

The use of TIM vs. Solder won't make a difference on the life of the chip. Before intel started soldering the die to IHS there was lots chips used TIM. There are plenty of chips running for 10+ years with TIM. Since Intel hasn't said anything it is unfair to say that intel didn't solder the chips just to save money. There maybe something else which may have to do with the 22nm fab or tri gate transistors... etc. Just playing devils(intel's) advocate here.

but IMO intel used TIM to cut costs and boost profit.

Don't know about older CPUs but if it is correct that it is to save a few pennies on K versions, then its criminal of Intel. I can see the logic of using TIM instead of solders on CPUs with locked multipliers but to do so in K version, ie for over-clocking is insane, especially when I have paid a premium over the non-K IB i5.

A 3.5gm syringe of AS5 cost under US$7 at a major online store and will cover 6-10 large CPUs. That makes under US100c per IHS...even cheaper if buying wholesale! Intel cannot be that tight-A**ed to save 100 pennies, right?

- Joined

- Jun 9, 2010

Don't know about older CPUs but if it is correct that it is to save a few pennies on K versions, then its criminal of Intel. I can see the logic of using TIM instead of solders on CPUs with locked multipliers but to do so in K version, ie for over-clocking is insane, especially when I have paid a premium over the non-K IB i5.

A 3.5gm syringe of AS5 cost under US$7 at a major online store and will cover 6-10 large CPUs. That makes under US100c per IHS...even cheaper if buying wholesale! Intel cannot be that tight-A**ed to save 100 pennies, right?

That's how companies work. Everything is about the bottom-line. Especially since amd isn't putting any pressure on them. But like I said earlier, since intel hasn't told us anything. We can say for sure that there isn't another reason they didn't solder.

i assumed the CLP would be orite after a year. i swear its only aluminium it eats through? The copper and nickle on the ISH shouldnt have any issues. Does anyone know what material the surface of the core actually is?

I am in the chip business and yes, it is the back side of a silicon wafer if there is no metalization on it. See my post above about the Intel patent.

A review linked below says about Coollaboratory Liquid PRO, that "It''s particularly awesome with bare dies."

That is what the Ivy Bridge chip under the IHS is. It is a bare die. This terminology is plural for DICE, which is what Intel does to make a 12" silicon wafer with hundreds of CPUs on it. They dice it up into die which are individual CPU chips and put them in a package with a less than optimum TIM for OC enthusiasts in the case of Ivy Bridge.

The source for the comment quoted above is in the third review down by writer named "xrror" at the review tab at this link.

http://www.frozencpu.com/products/3...ry_Liquid_PRO_Thermal_Interface_Material.html

For the most accurate info on using this TIM with bare die under the Intel IHS, I'd get the answer straight from the TIM maker.

- Joined

- Dec 10, 2011

- Location

- Cádiz (Spain)

Well, it is liquid metal, so yea, it's the best thing you can find.

100 penniesx1 billion = $1billion...

So has Intel sold 1 billion Ivy Bridge cpus thus far?

I had no much time yesterday but I put SS on my cpu and I was able to boot with about 100MHz higher clock than before I replaced TIM under IHS. I have no idea what temps are exactly as board isn't showing anything below -20*C. I'm still using MX4 and probably today I will test some more.

- Joined

- Apr 11, 2010

- Location

- London, UK

hmmmmmm I am so tempted to just get a 3770k and some colab liquid pro. Just how hard is it to apply the thermal past to a die? Cos if it is that easy i might just chance it. If i could hit 5ghz on a 3770k i would upgrade. I could flog my 2700k to offset at least 70% of the price too!

NO XANDER STOP IT YOU DONT NEED IT! * slaps himself*

NO XANDER STOP IT YOU DONT NEED IT! * slaps himself*

- Joined

- Feb 6, 2011

So has Intel sold 1 billion Ivy Bridge cpus thus far?

So far no, Ivy Bridge are 3 month old!

But, Intel makes around $40/$45 billions/year (that's what, roughly 300/400 millions CPUs'/year?).

Moving to 22nm/tim technology for all of them (I guess...), make your math!

- Joined

- Nov 3, 2008

So I was thinking about buying an i7 and delidding my i5 but I would want to use IC Diamond. The stuff is thick and I am wondering if it might cause a core crush.

- Thread Starter

- #34

I was able to drop my vcore offset from +200 mV down 150 mV to +5 mV and have a stable system as evaluated by: 5 h of mprime large/FFTs, 2 h of continuous compiling, 2 h of systest 64M, and 2 h of linpack+gcc. Lower operating temps have their tangibles. This is @ 45x100. I'll now switch over to 47x100 to see if I can drop the vcore by a proportional amount and might try 48x100. Just wanted to update.

After some weird results I decided to check mount , reapply TIM etc and no matter in which way I set IHS or how many times I try if TIM is applied in best possible way I always get +/- 7*C between cores. Even when IHS isn't exactly in the center ( as it's sliding a bit 1-2mm here or there ) then temps are about the same. I'm still using MX4

Thanks for update graysky

Thanks for update graysky

- Thread Starter

- #38

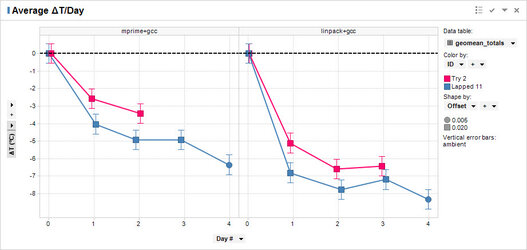

Interestingly, the lower offset (-150 mV) only translated into -1C drop across cores:

Squares are the offset of +0.020 V and circles are the offset of +0.005 V.

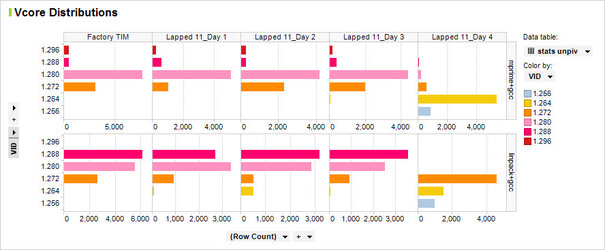

Here are a few visuals on the VID distributions. Remember, my script is sampling 30 times/sec and that on day 4, I dropped the offset by -150 mV:

Here it is in terms of raw counts:

Squares are the offset of +0.020 V and circles are the offset of +0.005 V.

Here are a few visuals on the VID distributions. Remember, my script is sampling 30 times/sec and that on day 4, I dropped the offset by -150 mV:

Here it is in terms of raw counts:

- Joined

- Jun 16, 2001

I love the scientific approach you took here and how you used the linux script to do your testing. There isn't enough Linux usage in the overclocker community imho. If there was I think the tools available to us would be much better.

Also as I understand it AS5 has been eclipsed by a bunch of different compounds. I think I saw somewhere else where the Ivy Bridge TIM was replaced will Coollabratory Pro LiquiCool and got a 12C drop. All in all, still a significant improvement.

Also as I understand it AS5 has been eclipsed by a bunch of different compounds. I think I saw somewhere else where the Ivy Bridge TIM was replaced will Coollabratory Pro LiquiCool and got a 12C drop. All in all, still a significant improvement.

Similar threads

- Replies

- 25

- Views

- 1K