-

Welcome to Overclockers Forums! Join us to reply in threads, receive reduced ads, and to customize your site experience!

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

possible unlock of superlock procs

- Thread starter bulk88

- Start date

- Joined

- Jul 29, 2001

This unlock depends on the motherboard. Actually its not even an unlock, but a work around. This thing only works on VIA and SiS chipsets, while on the AMD chipsets its a bit more tricky and on the nvidia chipsets its impossible.

I've tried it on my dead Tbred, and although the chip itself was unlocked it doesn't matter that much as this is a completely different way of changing multipliers, on my KT266A board, and it was pretty neat changing multipliers on the fly.

I've tried it on my dead Tbred, and although the chip itself was unlocked it doesn't matter that much as this is a completely different way of changing multipliers, on my KT266A board, and it was pretty neat changing multipliers on the fly.

- Thread Starter

- #184

It DOES work on locked chips. And I can change them to whatever (up 24x or down to 4x) will be stable. Heck I have a Duron running at 22x100FSB that is multiplier locked.dumbfish said:but it never did work on a locked chip.unless im missing something here.i mean it worked as far as it thought it was a mobile but that didnt mean he successfully changed the multi with stability.

What we are doing is using a different path to the mutiplier unit, the path that allows mobile processors to switch their speeds. Also you can go HIGHER than what L3 or the factory lcoked multiplier is. You still cant use your MB BIOS to change multiplier unfortuantly. But you use a program once your in windows.

- Joined

- Sep 22, 2003

sticky?

- Thread Starter

- #187

Maybe but I would need to rewrite the first message to have intructions on how to do the mod and I am not very good at it. Maybe someone can write the instrucations on how to do that.hrhrhrFOOT said:sticky?

- Joined

- Jan 12, 2004

- Location

- Menthol Island

Petr said:It is bit 0 of register 44h. Thanks!

Don't you want to be the second most famous in this unlocking effort (after me)? You have nForce 2, I know the bit that should enable FID_Change... just it doesn't work. Find solution and you will be king.

DFI Tech already told me nForce2 Chipset have some bug supporting changging multiplier on Fly(After system boot)....

if u know the register to set... why dont u try set it before system boot?

- Thread Starter

- #189

DFI told me that it was only VIA DFI boards taht can do that when I spoke to him some time ago. Well that would require a BIOS mod or does it need to be done in DOS and then soft reboot or boot record load win2k? Cuz the register stuff I did was in Win2k no SPs (I dont think it makes a difference).lemak said:DFI Tech already told me nForce2 Chipset have some bug supporting changging multiplier on Fly(After system boot)....

if u know the register to set... why dont u try set it before system boot?

- Joined

- Jan 12, 2004

- Location

- Menthol Island

bulk88 said:DFI told me that it was only VIA DFI boards taht can do that when I spoke to him some time ago. Well that would require a BIOS mod or does it need to be done in DOS and then soft reboot or boot record load win2k? Cuz the register stuff I did was in Win2k no SPs (I dont think it makes a difference).

Emm.. ok... if u want to mod WPCREDIT setting.. i can help u hack the bios and inject it as ISA rom... or epa coder routine.. or BPL Routine

if it involve FID and VID.. i need to do some reading first how the protocol is be done... Have any link?

WPCREDIT protocol.. i can done it now...

that mean it will set the setting before windows boot...

even before system boot up (BPL Hacking) or after boot EPA Coder Routine or ISA ROM routine hacking....

just let me know if u know which register to be patch....

- Joined

- Nov 10, 2003

- Location

- Canberra, Down Under

The problem is with the nForce chipsets not supporting the disconnected state that is required for a PowerNow transition. No amount of register-tweaking/bios-patching will fix that.

- Joined

- Jan 12, 2004

- Location

- Menthol Island

emboss said:The problem is with the nForce chipsets not supporting the disconnected state that is required for a PowerNow transition. No amount of register-tweaking/bios-patching will fix that.

emm... i didnt plan to do power now on nforce2

what i intend to do is unlock superlock processor with bios mod

inject a new code before Northbridge set the multiplier routine

- Thread Starter

- #193

Just wondering, how do you know that? and how sure are you? and howcome if ever other last manufactuer included it, why didnt nvidia? What about the registers (nVidia: nForce 2 (reg. E7, bit 4 = FID_Change Detect; reg. 6F, bit 4 = Halt Disconnect) - But there is high change this won't work, good solution hasn't been found to this date.) from http://www.cpuheat.wz.cz/html/Tweaks.htm ).??emboss said:The problem is with the nForce chipsets not supporting the disconnected state that is required for a PowerNow transition. No amount of register-tweaking/bios-patching will fix that.

Was is a manufacturing flaw that could be fixed with a revision, or they were never included from day 1?

I deep down inside still hope the nforces have power now support and I dont give up hope.

- Joined

- Nov 10, 2003

- Location

- Canberra, Down Under

I'm not 100% sure, but I've talked to a couple of (supposed, though it's hard to be sure) motherboard designers via email. They basically said that nVidia's official line to them was that PowerNow was not supported on the nForce 1 and 2 chipsets. One mentioned that the northbridge correctly handles the bus disconnect but then does not respond when the CPU tries to reconnect (so the computer halts).

I suppose there possibly could be a way to make the northbridge work correctly, but if the motherboard manufacturers (who have full access to the nForce tech docs) can't figure it out, I'd say that it's unlikely that anyone outside of them (who don't have access to pretty much any of the low-level docs, either from AMD or nVidia) would be able to do it.

I can only speculate as to why it was not included, since nVidia doesn't really want to talk about it for some reason My main guess is that it's due to the nForce 1 and 2 chipsets being very much designed for high-performance. There's only so much design time available in a project (more or less

My main guess is that it's due to the nForce 1 and 2 chipsets being very much designed for high-performance. There's only so much design time available in a project (more or less  ) and they possibly concentrated on performance and neglected to get the power saving features implemented correctly.

) and they possibly concentrated on performance and neglected to get the power saving features implemented correctly.

Oh, and lemak: the only known way to set the multiplier to anything but default on an Athlon is through the BP_FID pins. The northbridge has nothing to do with it{*}. This is how all motherboards that support multiplier changes do it. However, the BP_FID pins (along with the whole L1/L3 setup) no longer have any effect on the startup multiplier of the CPU. So you can try to modify the SIP stream (oh, and if you find any docs that actually provide any information on the SIP packets, I would be most interested ) but I don't think you'll have a lot of luck with it ...

) but I don't think you'll have a lot of luck with it ...

{*} OK, the northbridge RECEIVES the multiplier as part of the SIP protocol, but I don't beleive it's sent by the northbridge at any point in time. Lacking the SIP docs, I can't be sure though.

I suppose there possibly could be a way to make the northbridge work correctly, but if the motherboard manufacturers (who have full access to the nForce tech docs) can't figure it out, I'd say that it's unlikely that anyone outside of them (who don't have access to pretty much any of the low-level docs, either from AMD or nVidia) would be able to do it.

I can only speculate as to why it was not included, since nVidia doesn't really want to talk about it for some reason

Oh, and lemak: the only known way to set the multiplier to anything but default on an Athlon is through the BP_FID pins. The northbridge has nothing to do with it{*}. This is how all motherboards that support multiplier changes do it. However, the BP_FID pins (along with the whole L1/L3 setup) no longer have any effect on the startup multiplier of the CPU. So you can try to modify the SIP stream (oh, and if you find any docs that actually provide any information on the SIP packets, I would be most interested

{*} OK, the northbridge RECEIVES the multiplier as part of the SIP protocol, but I don't beleive it's sent by the northbridge at any point in time. Lacking the SIP docs, I can't be sure though.

- Thread Starter

- #195

emboss said:I'm not 100% sure, but I've talked to a couple of (supposed, though it's hard to be sure) motherboard designers via email. They basically said that nVidia's official line to them was that PowerNow was not supported on the nForce 1 and 2 chipsets. One mentioned that the northbridge correctly handles the bus disconnect but then does not respond when the CPU tries to reconnect (so the computer halts).

I suppose there possibly could be a way to make the northbridge work correctly, but if the motherboard manufacturers (who have full access to the nForce tech docs) can't figure it out, I'd say that it's unlikely that anyone outside of them (who don't have access to pretty much any of the low-level docs, either from AMD or nVidia) would be able to do it.

I can only speculate as to why it was not included, since nVidia doesn't really want to talk about it for some reasonMy main guess is that it's due to the nForce 1 and 2 chipsets being very much designed for high-performance. There's only so much design time available in a project (more or less

) and they possibly concentrated on performance and neglected to get the power saving features implemented correctly.

Oh, and lemak: the only known way to set the multiplier to anything but default on an Athlon is through the BP_FID pins. The northbridge has nothing to do with it{*}. This is how all motherboards that support multiplier changes do it. However, the BP_FID pins (along with the whole L1/L3 setup) no longer have any effect on the startup multiplier of the CPU. So you can try to modify the SIP stream (oh, and if you find any docs that actually provide any information on the SIP packets, I would be most interested) but I don't think you'll have a lot of luck with it ...

{*} OK, the northbridge RECEIVES the multiplier as part of the SIP protocol, but I don't beleive it's sent by the northbridge at any point in time. Lacking the SIP docs, I can't be sure though.

Now I know this is immpossible if you dont have a team of AMD engineers and a couple wheelbarrows of NDA/and internal confiddential books on the ahtlon, but can you change the multiplier of the CPU, like hard wire it in or something, by doing a microcode update into the CPU?

- Joined

- Nov 10, 2003

- Location

- Canberra, Down Under

I'd be surprised if a microcode update would do the trick. I think the way microcode operates in Intel chips is that it's copied (when the chip powers on) to volatile memory (effectively cache RAM). The microcode update is applied during POST by the BIOS, after the CPU has already began operating. Hence, the changes only apply until a chip reset, when the chip reloads the memory from the microcode ROM. It may be possible to enable features like PowerNow (or hyperthreading, if you're on the Intel side) through a microcode update, but I don't think it's possible to make the chip change it's power-on sequence through a microcode update. Of course, this all assumes a lot about the capability of the microcode rom, none of which really applies if it just feeds a sequence of basic micro-ops into the instruction stream.

Of course, AMD's implementation could be different. In fact, I've never seen any reference to being able to do a microcode update on an Athlon, though it does support the IA32 microcode update MSRs. I might try shoving some random data into them a bit to see what they do Given AMD's strong flash ram capability, I would not be entirely surprised if the microcode was stored in flash RAM, but on the other hand AMD has never issued a microcode update, so I would guess that the Athlon has no microcode update capability.

Given AMD's strong flash ram capability, I would not be entirely surprised if the microcode was stored in flash RAM, but on the other hand AMD has never issued a microcode update, so I would guess that the Athlon has no microcode update capability.

Of course, AMD's implementation could be different. In fact, I've never seen any reference to being able to do a microcode update on an Athlon, though it does support the IA32 microcode update MSRs. I might try shoving some random data into them a bit to see what they do

- Joined

- Jan 12, 2004

- Location

- Menthol Island

TicTac & CodeRed write this program to tweak nForce2 setting in windows environment..

hope this help nforce2 user ....

nForce2 Tweaker 0.25B

- For all nForce2 board...

DownloadLink:-

http://users.tpg.com.au/spark69/NF2Tweaker/nf2tweaker025b.zip

http://forum.abit-usa.com/attachment.php?s=&postid=379291

hope this help nforce2 user ....

nForce2 Tweaker 0.25B

- For all nForce2 board...

DownloadLink:-

http://users.tpg.com.au/spark69/NF2Tweaker/nf2tweaker025b.zip

http://forum.abit-usa.com/attachment.php?s=&postid=379291

Attachments

- Thread Starter

- #198

To Emboss:

I read in the Athlon datasheets about each processor having a JTAG interface, I read a little bit more and realized that thats a bios/flash chip/pin tester/SMbus/addresible registers wannabe interface. Is tehre any way to put in a new multiplier with this interface, or if its mb accesible or will u need to solder the cpu socket?

I read in the Athlon datasheets about each processor having a JTAG interface, I read a little bit more and realized that thats a bios/flash chip/pin tester/SMbus/addresible registers wannabe interface. Is tehre any way to put in a new multiplier with this interface, or if its mb accesible or will u need to solder the cpu socket?

- Joined

- Jan 12, 2004

- Location

- Menthol Island

bulk88 said:To Emboss:

I read in the Athlon datasheets about each processor having a JTAG interface, I read a little bit more and realized that thats a bios/flash chip/pin tester/SMbus/addresible registers wannabe interface. Is tehre any way to put in a new multiplier with this interface, or if its mb accesible or will u need to solder the cpu socket?

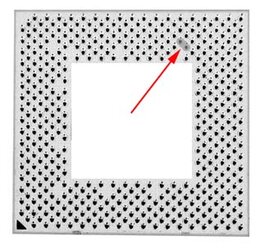

Here how they unlocked the superlock chip

http://www.3dcool.com/?module=product&sku=SSA1

cheers

- Joined

- Jan 12, 2004

- Location

- Menthol Island